BLUEFISH Functional Specification

14 July 1978 Art Lim

### Table of Contents

| Section | 1 |   |   | PDI | P | 11/68 | Overview |

|---------|---|---|---|-----|---|-------|----------|

|         |   | _ | _ |     |   |       |          |

- 1.1 Introduction

- 1.2 11/68 Internal I/O Page Address Register Index

## Section 2 PDP 11/68 Processor

- 2.1 Base Processor Instructions

- Table 2.1 Addressing Modes

- Table 2.2 Single Operand Instructions

- Table 2.3 Double Operand Instructions

- Table 2.4 Processor Control Instructions

- Table 2.5 Miscellaneous Instructions

- Table 2.6 Condition Code Operators

- Table 2.7 Programming Difference List

- 2.2 Processor Control Registers

- 2.3 Aborts, Traps, Interrupts

- 2.4 Memory Management

- 2.5 Cache/Memory Operations

- Section 3 Floating Point Processor/Instructions

- Section 4 Memory System To be specified

- Section 5 Console

- Sections 6 Software Issues

- Appendix A Midrange Systems Console Functional Specification

### PROJECT BLUEFISH (PDP 11/68)

#### 1.0 Introduction

BLUEFISH represents the new high end of the PDP-11 architecture offering performance in excess of the 11/74 (target at 1.5 times 11/74 base processor) at a significantly reduced cost ( $\frac{1}{2}$  transfer cost of 11/74). Multiprocessor hooks will be incorporated within the hardware to permit the multiprocessor multi-port memory configuration of the 11/74.

Full 11/74 functionality will be provided with the exception of the following:

System I/D Register 17 777 764

System Size Register 17 777 760 -- 17 777 762

Trap functions within Memory Management

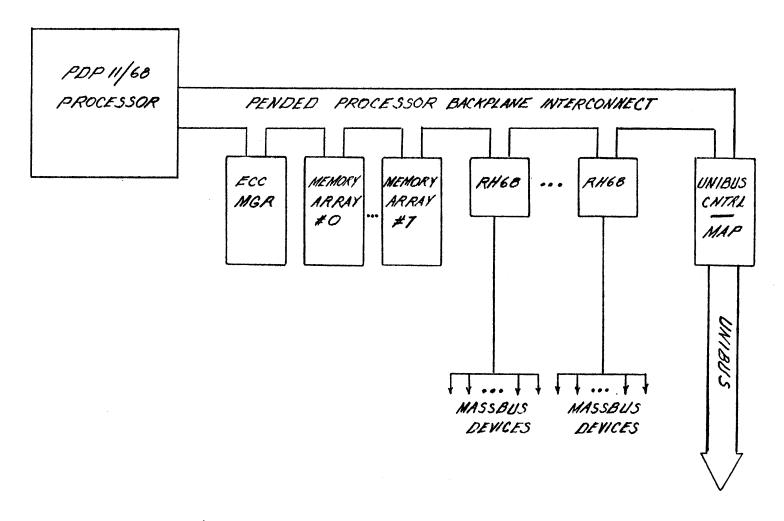

The PDP 11/68 system configuration is illustrated in figure #1. Communication between functional units of the system is provided through a high bandwidth synchronous backplane interconnect called the PPBI.

Mass bus peripherals will communicate with primary memory through RH68 controllers compatible with RH70 controllers of the 11/70.

The Unibus mapping functions, Unibus arbitration as well as translation of signals from Unibus to PPBI is provided by the Unibus Controller (UBC).

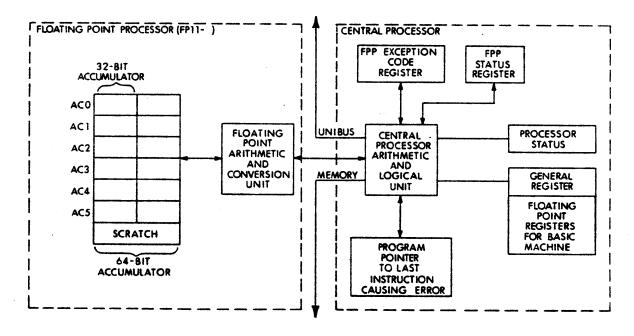

BLUEFISH will provide the Commercial Instruction (DEC STD 168 Revision B) and both integral and accelerated versions of floating point containing the full FP11 instruction set. The cache buffer provides for 2040 bytes of data storage configured in set size 2 and block size 2.

This document has been assembled as a preliminary software reference guide for the Bluefish processor. It's purpose is to summarize the software compatibilities, point out any instructions and in general to eliminate any confusion that may arise in the upgrade of DEC operating systems and diagnostics.

Please review the contents of this document primarily focussing on the format of control and status registers that reflect processor specific functions, trap vectors, and priorities as well as the difference list which identifies the differences in the implementation of functions by different processes in the PDP-11 family. (Table 2-7).

1.2 11/68 Internal I/O Page Address Register Index

| Address                  | Register                               | Section Described |

|--------------------------|----------------------------------------|-------------------|

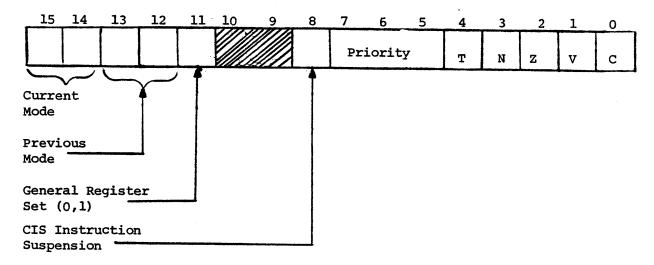

| 17 777 776               | Processor Status Word                  | Program Control   |

| 17 777 774               | Stack Limit                            | Program Control   |

| 17 777 772               | Program Interrupt Request              | Program Control   |

| 17 777 77Ø               | Micro break                            |                   |

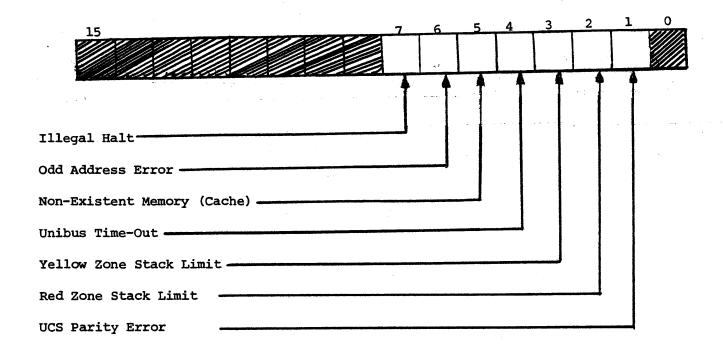

| 17 777 766               | CPU Error                              | Program Control   |

| 17 777 764               | System I/D                             | Not Implemented   |

| 17 777 762               | Upper System Size                      | Not Implemented   |

| 17 777 76Ø               | Lower System Size                      | Not Implemented   |

| 17 777 754               | Cache/Memory Maintenance<br>Register Ø | Cache/Memory      |

| 17 777 752               | Cache/Memory Maintenance<br>Register 1 | Cache/Memory      |

| 17 777 75Ø               | Cache/Memory Maintenance<br>Register 2 | Cache/Memory      |

| 17 777 746               | Cache Control                          | Cache/Memory      |

| 17 777 744               | Cache/Memory System Error              | Cache/Memory      |

| 17 777 742               | High Error Address                     | Cache/Memory      |

| 17 777 740               | Low Error Address                      | Cache/Memory      |

| 17 777 696<br>17 777 6ØØ | User I/D PAR/PDR                       | Memory Management |

| 17 777 576               | Memory Management Register 2           | Memory Management |

| 17 777 574               | Memory Management Register 1           | Memory Management |

| 17 777 572               | Memory Management Register 0           | Memory Management |

| 17 777 57ø               | Console and Display                    | Console           |

| 17 772 576               | Memory Management Register 3           | Memory Management |

| <u>Address</u>           | Register               | Section Described |

|--------------------------|------------------------|-------------------|

| 17 772 376<br>17 772 3ØØ | Kernal I/D PAR/PDR     | Memory Management |

| 17 772 276<br>17 772 2ØØ | Supervisor I/D PAR/PDR | Memory Management |

PDP11/68 SYSTEM CONFIGURATION

#### Section 2 PDP 11/68 Processor

#### 2.1 Base Processor Instructions

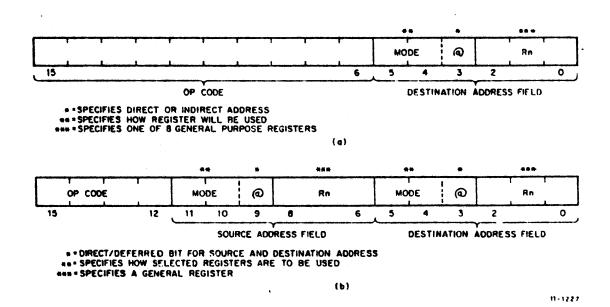

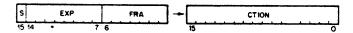

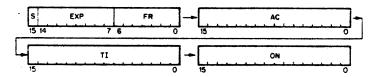

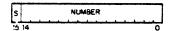

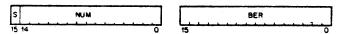

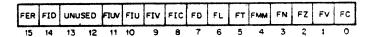

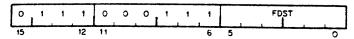

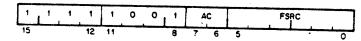

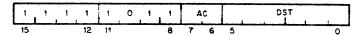

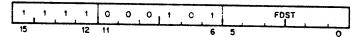

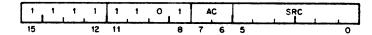

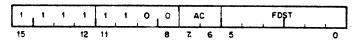

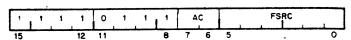

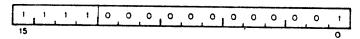

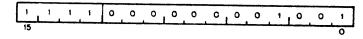

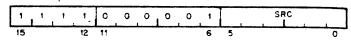

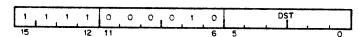

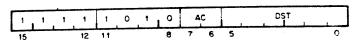

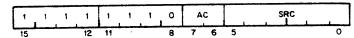

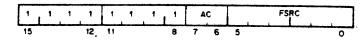

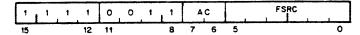

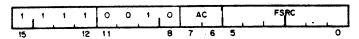

Figure 2-1 Addressing Mode Instruction Formats

# Addressing Modes

| Mode . | Binary<br>Code | Name          | Assembler<br>Syntax* | Function                                                                                                                                                                                                                              |

|--------|----------------|---------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •      |                | D:            | irect Modes          |                                                                                                                                                                                                                                       |

| 0      | 000            | Register      | Rn                   | Register contains operand.  Operations performed on registers in byte mode refer to the low order byte (bits <7:0>) of the register.                                                                                                  |

| 2      | 010            | Autoincrement | (Rn)+                | Register contains address of operand. Register contents incremented after reference. Registers 6 (SP) and 7 (PC) are always incremented by 2 after reference. RØ - R5 are incremented by 2 for word and by 1 for byte instructions.   |

| 4      | 100            | Autodecrement | -(Rn)                | Register contents decremented before reference. Register contains address of operand. Registers 6 (SP) and 7 (PC) are always decremented by 2 before reference. RØ - R5 are decremented by 2 for word and by 1 for byte instructions. |

| 6      | 110            | Index         | X (Rn)               | Value X (stored in a word following the instruction) is added to (Rn) to produce address of operand. Neither X nor (Rn) is modified.                                                                                                  |

# Addressing Modes (con't)

## Deferred Modes

| 1 | 001 | Register<br>Deferred      | @Rn or (Rn) | Register contains the address of the operand.                                                                                                                                                      |

|---|-----|---------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | 011 | Autoincrement<br>Deferred | @(Rn)+      | Register is first used as a pointer to a word containing the address of the operand, then incremented (always by two, even for byte instructions).                                                 |

| 5 | 101 | Autodecrement<br>Deferred | @- (Rn)     | Register is decremented (always<br>by two, even for byte instruc-<br>tions) and then used as a<br>pointer to a word containing<br>the address of the operand.                                      |

| 7 | 111 | Index Deferred            | @x (Rn)     | Value X (stored in the memory word following the instruction) and (Rn) are added and the sum is used as a pointer to a word containing the address of the operand. Neither X nor (Rn) is modified. |

Table 2-1 Addressing Modes (cont)

|      |                |                   | t was to the court   |                                                                                                    |

|------|----------------|-------------------|----------------------|----------------------------------------------------------------------------------------------------|

| Mode | Binary<br>Code | Name              | Assembler<br>Syntax* | Function                                                                                           |

|      |                |                   | PC Addressing        |                                                                                                    |

| 2    | 010            | Immediate         | #n                   | Operand follows instruction.                                                                       |

| 3    | 011            | Absolute          | @#A                  | Absolute address follows instruction.                                                              |

| 6    | 110            | Relative          | A                    | Address of A, relative to the instruction, follows the instruction.                                |

| 7    | 111            | Relative Deferred | @A                   | Address of location containing address of A, relative to the instruction, follows the instruction. |

<sup>\*</sup> Rn = Register

# PDP 11/68 INSTRUCTIONS

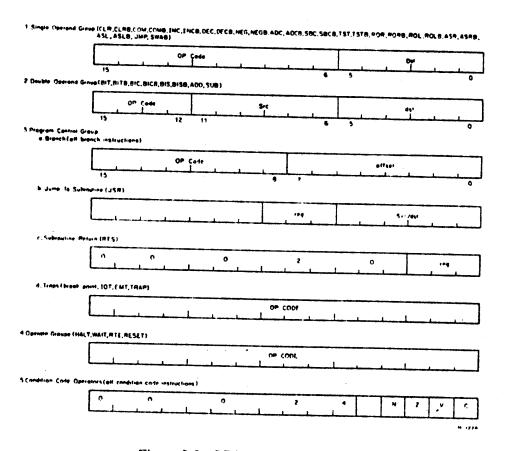

PDP 11/68 instructions can be divided into five groups:

- Single-Operand Instructions (shifts, multiple precision instructions, rotations)

- Double-Operand Instructions (arithmetic and logical instructions)

- Program Control Instructions (branches, subroutines, traps)

- 4. Operate Group Instructions (processor control operations)

- Condition Code Operators (processor status word bit instructions)

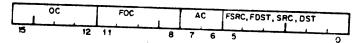

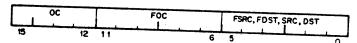

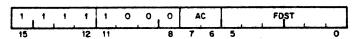

Tables 2-2 through 2-6 list each instruction, including byte instructions for the respective instruction groups. Figure 2-2 shows the six different instruction formats of the instruction set, and the individual instructions in each format.

X, n, A = next program counter (PC) word (constant)

Table 2-2 Single Operand Instructions

| Mnemonic                   | OP Code           | Operation         | Condition Codes                                                                                                                      | Description                                                                                                                                                           |

|----------------------------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR<br>CLRB<br>Clear       | 0050DD*<br>1050DD | (dst = 0          | N. cleared Z. set V. cleared C. cleared                                                                                              | Contents of specified destination are replaced with zeroes.                                                                                                           |

| COMB<br>COMB<br>Complement | 0051DD<br>1051DD  | (dst) ← n (dst)   | N: set if most significant bit of result is 0 Z: set if result is 0 V: cleared C: set                                                | Replaces the contents of the destination address by it car logical complement (each bit equal to 0 set and each bit equal to 1 cleared).                              |

| INC<br>INCB<br>Increment   | 0052DD<br>1052DD  | (dst) (dst) +     | N: set if result is less than 0 Z: set if result is 0 V: set if (dst) was 077777 C: not affected                                     | Add 1 to the contents of the destination.                                                                                                                             |

| DEC<br>DECB<br>Decrement   | 0053DD<br>1053DD  | (dst) ← (dst) - 1 | N: set if result is less than 0<br>Z: set if result is 0<br>V: set if (dst) was 100000<br>C: not affected                            | Subtract 1 from the contents of the destination.                                                                                                                      |

| NEG<br>NEGB<br>Negate      | 0054DD<br>1054DD  | (dst) ← -(dst)    | No set if result is less than 0 Z: set if result is 0 V: set if result is 100000 C: cleared if result is 0                           | Replaces the contents of the destination address by its 2's complement. Note that 100000 is replaced by itself.                                                       |

| ADC<br>ADCB<br>Add Carry   | 0055DD<br>1055DD  | (dst) ← (dst) + C | N: set if result is less than 0  Z. set if result is 0  V: set if (dst) is 077777 and  C is 1  C: set if (dst) is 177777 and  C is 1 | Adds the contents of the C-bit into the destination. This permit the carry from the addition of the low-order words, bytes to be carried into the high-order results. |

Table 2-2 Single Operand Instructions (Cont)

| Mnemonic                      | OP Code          | Operation                             | Condition Codes                                                                                                                                           | Description                                                                                                                                                                                                    |

|-------------------------------|------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBC<br>SBCB<br>Subtract Carry | 0056DD<br>1056DD | (dst) ← (dst) -C                      | N: set if result is less than 0 Z: set if result is 0 V: set if (dst) was 100000 C: cleared if (dst) is 0 and C is 1                                      | Subtracts the contents of the C-bit from the destination. This permits the carry from the subtraction of the low order words bytes to be subtracted from the high-order part of the result.                    |

| TST<br>TSTB<br>Test           | 0057DD<br>1057DD | (dst) ← (dst)                         | N: set if result is less than 0 Z: set if result is 0 V: cleared C: cleared                                                                               | Sets the condition codes N and Z according to the contents of the destination address.                                                                                                                         |

| ROR<br>RORB<br>Rotate Right   | 0060DD           | (dst) ← (dst) rotate right one place. | N: set if high-order bit of the result is set Z: set if all bits of result are 0 V: loaded with the exclusive-OR of the N-bit and the C-bit as set by ROR | Rotates all bits of the destination right one place. The low-order bit is loaded into the C-bit and the previous contents of the C-bit are loaded into the high-order bit of the destination.                  |

| OL<br>OLB<br>otate Left       | 0061DD<br>1061DD | (dst) ← (dst) rotate left one place   | N: set if the high order bit of the result word is set (result < 0); cleared                                                                              | Rotate all bits of the destination left one place. The high-order bit is loaded into the C-bit of the status word and the previous contents of the C-bit are loaded into the low-order bit of the destination. |

Table 2-2 Single Operand Instructions (Cont)

| Mnemonic                                 | OP Code          | Operation                                     | Condition Codes                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASR<br>ASRB<br>Arithmetic<br>Shift Right | 0062DD<br>1062DD | (dst) ← (dst) shifted one place to the right. | N: set if the high order bit of the result is set (result < 0), cleared otherwise  Z. set if the result = 0, cleared otherwise V: loaded from the exclusive- OR of the N-bit and C-bit (as set by the completion of the shift operation) C: loaded from low order bit of the destination       | Shifts all bits of the destination right one place. The high-order bit is replicated. The C-bit is loaded from the low-order bit of the destination. ASR performs signed division of the destination by two.                                                       |

| ASL<br>ASLB<br>Arithmetic<br>hift Left   | 0063DD<br>1063DD | (dst) — (dst) shifted one place to the left.  | N: set if high-order bit of the (result < 0); cleared otherwise  Z. set if the result = 0; cleared otherwise  V loaded with the exclusive-OR of the N-bit and C-bit and C-bit and C-bit (as set by the completion of the shift operation)  C loaded with the high-order bit of the destination | Shifts all bits of the destination left one place. The low-order bit is loaded with a 0. The C-bit of the status word is loaded from the high-order bit of the destination. ASL performs a signed multiplication of the destination by 2 with overflow indication. |

|                            |         |                                                                                            |                                                                                                                                                                                                                                                                         | ,                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|---------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic                   | Op Code | Operation                                                                                  | Condition Codes                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                |

| ASH<br>Arithmetic<br>Shift | 072RSS  | R R Shifted Arithmetically NN places to right or left Where NN = (src)                     | <ul> <li>N: set if result&lt;0; cleared otherwise.</li> <li>Z: set if result = 0; cleared otherwise.</li> <li>V: set if sign of register changed during shift; cleared otherwise.</li> <li>C: loaded from last bit shift out of register.</li> </ul>                    | The contents of the register are shifted right or left the number of times specified by the source operand. The shift count is taken as the low-order 6 bits of the source operand. This number ranges from -32 to +31. Negative is a right shift and positive is a left shift.                                                                                                            |

| ASHC<br>Arithmetic         |         |                                                                                            |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                            |

| Shift Combined             | 073RSS  | R, Rvl+ R, Rvl The double word is shifted NN places to the right or left, where NN = (src) | <pre>N: set if result &lt;0; cleared otherwise. Z: set if result = 0; cleared otherwise. V: set if sign bit changes during shift; cleared otherwise. C: loaded with high-order bit when right shift (loaded with the last bit shifted out of the 32-bit operand).</pre> | operand). This number ranges from -32 to +31. Negative is right shift and positive is a left shift. Condition codes are affected by the 32-bit result. Bits <31:16> of the result are stored in R if R is even. Bits <15:0> are stored in Rvl. R can be odd or even.  If R is odd, the left shift works like a 16-bit left shift. A right shift works like a 16-bit right rotate for shift |

|                            |         |                                                                                            |                                                                                                                                                                                                                                                                         | counts up to 16. If a right shift by more than 16-bits is specified the operation results in an arithmetic right shift by an amount equal to the shift count less 16.                                                                                                                                                                                                                      |

| SXT<br>Sign Extend         | 0067DD  | (dst)← 0 if N bit<br>is clear<br>(dst)← -l N bit<br>is set                                 | <ul><li>N: unaffected</li><li>Z: set if N bit clear</li><li>V: cleared</li><li>C: unaffected</li></ul>                                                                                                                                                                  | If the condition code bit N is set then a -1 is placed in the destination operand:  If N bit is clear, then a 0 is placed in the destination operand. This instruc-                                                                                                                                                                                                                        |

the destination operand. This instruction is particularly useful in multiple precision arithmetic because it permits the sign to be extended through multiple

words.

Table 2-2 Single Operand Instructions (Cont)

| Mnemonic          | OP Code | Operation                      | Condition Codes                                                                                                                                                            | Description                                                                                                |

|-------------------|---------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| SWAB<br>Swap Byte | 0003DD  | Byte 1/Byte 0<br>Byte 0/Byte 1 | N: set if high-order bit of low-order byte (bit 7) of result is set; cleared otherwise.  Z: set if low-order byte of result = 0; cleared otherwise.  V: cleared C: cleared | Exchanges high-order byte and low-order byte of the destination word (destination must be a word address). |

Table 2-3 Double Operand Instructions

| Maemonic                    | OP Code           | Operation                                      | Condition Codes                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|-------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV 3<br>Move               | 01SSDD*<br>11SSDD | (dst) ← (src) <sup>†</sup>                     | N: set if (src) < 0, cleared otherwise Z: set if (src) = 0, cleared otherwise V: cleared C: not affected                                                                                                                                                                                                                                   | Word: Moves the source operand to the destination location. The previous contents of the destination are lost. The source operand is not affected.  Byte: Same as MOV The MOVB to a resistor (unique among byte instructions) extends the most significant bit of the low order byte (sign extension). Otherwise MOVB operates on bytes exactly as MOV operates on words.                                  |

| CMP<br>CMP3 cmp8<br>Compute | 02SSDD<br>12SSDD  | (src) - (dst) [in detail. (src) + ~ (dst) + 1] | N: set if result < 0. cleared otherwise  Z. set if result = 0; cleared otherwise  V: set if there was arithmetre overflow (i.e., operands were of opposite signs and the sign of the destination was the same as the sign of the result); cleared otherwise.  C: cleared if there was a carry from the most significant bit of the result. | Compares the source and destination operands and set—the condition codes—which may then be used for arithmetic and logical conditional branches. Both operands are unaffected. The only action is to set the condition codes. The compare is customarily followed by a conditional branch instruction. Yes that unlike the subtract instruction the order of operation is (src) - (dst) not (dst) - (src). |

Table 2-3 Double Operand Instructions (Cont)

| Mnemonic                 | OP Code          | Operation                  | Condition Codes                                                                                                              | Description                                                                                                                                                                                                                                                                                                       |

|--------------------------|------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT<br>BITB<br>Bit Test  | 03SSDD<br>13SSDD | (src)∧(dst)                | N: set if high order bit of result set; cleared otherwise Z: set if result = 0; cleared otherwise V: cleared C: not affected | Performs logical AND comparison of the source and destination operands and modifies condition codes accordingly. Neither the source nor destination operands are affected. The BIT instruction may be used to test whether any of the corresponding bits that are set in the destination are clear in the source. |

| BIC<br>BICB<br>Bit Clear | 04SSDD<br>14SSDD | (dst) ← ~ (src)<br>^ (dst) | N: set if high order bit of result set; cleared otherwise Z: set if result = 0; cleared otherwise V: cleared C: not affected | Clears each bit in the destination that corresponds to a set bit in the source. The original contents of the destination are lost. The contents of the source are unaffected.                                                                                                                                     |

| BIS<br>BISB<br>Bit Set   | 05SSDD<br>15SSDD | (dst) ← (src)<br>∧ (dst)   | N: set if high order bit of result set, cleared otherwise Z: set if result = 0; cleared otherwise V: cleared C: not affected | Performs inclusive-OR operation between the source and destination operands and leaves the result at the destination address; i.e., corresponding bits set in the destination. The contents of the destination are lost.                                                                                          |

| ADD<br>Add ·             | 06SSDD           | (dst) ← (src)<br>+ (dst)   | N: set if result 0, cleared otherwise  Z: set if result = 0; cleared otherwise                                               | Adds the source operand to the destination operand and stores the result at the destination address. The original contents of the destination are lost. The contents of the source are not affected. Two's complement addition is performed.                                                                      |

Table 2-3 Double Operand Instruction (Cont)

| Mnemonic        | OP Code  | Operation                                                           | Condition Codes                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                          |

|-----------------|----------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD (Cont)      |          |                                                                     | V: set if there was arithmetic overflow as a result of the operation (that is, both operands were of the same sign and the result was of the opposite sign); cleared otherwise.  C: set if there was a carry from the most significant bit of the result; cleared other-                                          |                                                                                                                                                                                                                                                                                      |

|                 | •        | •                                                                   | wise.                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                      |

| SUB<br>Subtract | · 16SSDD | (dst) ← (dst) -<br>(src) in detail.<br>(dst) + ~ (src)<br>+ 1 (dst) | N: set if result < 0, cleared otherwise  Z: set if result = 0, cleared otherwise  V: set if there was arithmetic overflow as a result of the operation (i.e., if operands were of opposite signs and the sign of the source was the same as the sign of the result); cleared otherwise  C: cleared if there was a | Subtracts the source operand from the destination operand and leaves the result at the destination address. The original contents of the destination are lost. The contents of the source are not affected. In double precision arithmetic, the C-bit, when set, indicates a borrow. |

|                 |          |                                                                     | carry from the most<br>significant bit of the<br>result; set otherwise                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                      |

<sup>\*</sup> SS = source (uddress mode and register)

<sup>† (</sup>sta) = source contents

Table 2-3 Double Operand Instructions (Cont.)

| Mnemonic        | OP Code | Operation            | Condition Codes                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUL<br>Multiply | 070RSS  | R,Rvl +Rx(src)       | N: set if product is<0: cleared otherwise. Z: set if product is 0; cleared otherwise. V: cleared C: set if the result is less than -2 <sup>15</sup> or greater than or equal to 2 <sup>15</sup> -1.                                                                                             | The contents of the destination register and source taken as two's complement integers are multiplied and stored in the destination register and the succeeding register (if R is even). If R is odd, only the low-order product is stored. Assembler syntax is: MUL S,R.  (Note that the actual destination is R,Rvl which reduces to just R when R is odd.)                                                                                                                                                                                                                        |

| DIV<br>Divide   | 071RSS  | R,Rvl+R,Rvl<br>(src) | N: unpredictable if V is set. Set if quotient 0; cleared otherwise.  Z: unpredictable if V is set. Set if quotient =0; cleared otherwise.  V: set if source = 0 or overflow (quotient less than -2 <sup>15</sup> or greater than 2 <sup>15</sup> -1).  C: set if source = 0; cleared otherwise. | If division by zero is attempted the instruction is terminated and the destination operand is left unchanged. Otherwise, the 32-bit two's complement integer in R and Rvl is divided by the source operand. The quotient is left in R; the remainder in Rvl. Non-zero remainder always has the same sign as the dividend. If the quotient cannot be represented as a 16 bit two's complement integer, overflow occurs. In this case the instruction aborts and the contents of the destination registers are unpredictable If R is odd or if R6 is used the result is unpredictable. |

| XOR             | 074RDD  | (dst)←Rv(dst)        | <pre>N: set if the result &lt;0; cleared otherwise. Z: set if result=0; cleared otherwise. V: cleared C: unaffected</pre>                                                                                                                                                                       | The exclusive OR of the register and destination operand is stored in the destination address. Contents of register are unaffected. Assembler format is XOR R,D.                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 2-4 Program Control Instructions

| Mnemonic                                 | OP Code        | Operation                           | Condition Codes | Description                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------|----------------|-------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR<br>Branch                             | 000400<br>xxx† | PC ← PC + (2 × offset)              | Unaffected      | Provides a way of transferring program control within a range of -128 to +127 words with a one word instruction. It is an unconditional branch.                                                                                                                                                                                          |

| BNE<br>Branch if not<br>equal            | 001000<br>xxx  | PC ← PC + (2 × offset) if Z = 0     | Unaffected      | Tests the state of the Z-bit and causes a branch if the Z-bit is is clear. BNE is the complementary operation to BEQ. It is used to test inequality following a CMP, to test that some bits set in the destination were also in the source, following a BIT, and generally, to test that the result of the previous operation was not 0. |

| BEQ<br>Branch if equal                   | 001400<br>xxx  | PC ← PC + (2 × offset) if Z = 1     | Unaffected      | Tests the state of the Z-bit and causes a branch if Z is set. As an example, it is used to test equality following a CMP operation, to test that no bits set in the destination were also set in the source following a BIT operation, and generally, to test that the result of the previous operation was 0.                           |

| BGE<br>Branch if greater<br>han or equal | 002000<br>xxx  | PC - PC + (2 × offset) if N v V = 0 | Unaffected      | Causes a branch if N and V are either both clear or both set.  BGE is the complementary operation to BLT. Thus, BGE always causes a branch when it follows an operation that caused addition to two positive numbers. BGE also causes a branch on a 0 result.                                                                            |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic                                  | OP Code       | Operation                                 | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|---------------|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLT<br>Branch if less<br>than             | 002400<br>xxx | PC ← PC + (2 × offset) if N V = 1         | Unaffected      | Causes a branch if the exclusive-OR of the N- and V-bits are 1. Thus, BLT always branches following an operation that added two negative numbers, even if overflow occurred. In particular BLT always causes a branch if it follows a CMP instruction operating on a negative source and a positive destination (even if overflow occurred). Further, BLT never causes a branch when it follows a CMP instruction operating on a positive source and negative destination. BLT does not cause a branch if the result of the previous operation was 0 (without overflow). |

| BGT<br>Branch if greater<br>than          | 003000<br>xxx | PC ← PC + (2 × offset) if Z v (N ← V) = 0 | Unaffected      | Operation of BGT is similar to BGE, except BGT does not cause a branch on a 0 result.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BLE<br>Branch if less than<br>or equal to | 003400<br>xxx | PC ← PC + (2 × offset) if Z v (N → V) = 1 | Unaffected      | Operation is similar to BLT, but in addition will cause a branch if the result of the previous operation was 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BPL<br>Branch if plus                     | 100000<br>xxx | PC ← PC + (2 × offset) if N = 0           | Unaffected      | Tests the state of the N-bit and causes a branch if N is clear. BPL is the complementary operation of BMI.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MI<br>tranch if minus                     | 100400        | PC ← PC +<br>(2 × offset) if<br>N = 1     | Unaffected      | Tests the state of the N-bit and causes a branch if N is set. It is used to test the sign (most significant bit) of the result of the previous operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic                                                                   | OP Code       | Operation                             | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------|---------------|---------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BHI<br>Branch if higher                                                    | 101000<br>xxx | PC ← PC +<br>(2 × offset) if<br>C = 0 | Unaffected      | Causes a branch if the previous operation causes neither a carry nor a 0 result. This will happen in comparison (CMP) operation as long as the source has a higher unsigned value than the destination.                                                                                                                                                                                          |

| BLOS<br>Branch if lower<br>or same                                         | 101400<br>xxx | PC ← PC + (2 × offset) if C v Z =     | Unaffected      | Causes a branch if the previous operation caused either a carry or a 0 result. BLOS is the complementary operation to BHI. The branch occurs in comparison operations as long as the source is equal to or has a lower unsigned value than the destination. Comparison of unsigned values with the CMP instruction to be tested for "higher or same" and "higher" by a simple test of the C-bit. |

| BVC<br>Branch if V-bit<br>clear                                            | 102000<br>xxx | PC ← PC +<br>(2 × offset) if<br>V = 0 | Unaffected      | Tests the state of the V-bit and causes a branch if the V-bit is clear. BVC is complementary operation to BVS.                                                                                                                                                                                                                                                                                   |

| BVS<br>Branch if V-bit set                                                 | 102400<br>xxx | PC ← PC +<br>(2 × offset) if<br>V = 1 | Unaffected .    | Tests the state of V-bit (overflow) and causes a branch it the V-bit is set. BVS is used to detect arithmetic overflow in the previous operation.                                                                                                                                                                                                                                                |

| BCC<br>BHIS<br>Branch if carry<br>lear<br>Branch if higher<br>han the same | 103000<br>xxx | PC ← PC + (2 × offset) if C = 0       | Unaffected      | Tests the state of the C-bit and causes a branch if C is clear.  BCC is the complementary operation to BCS.                                                                                                                                                                                                                                                                                      |

| CS LO ranch if carry set ranch if lower                                    | 103400<br>xxx | PC PC + (2 × offset) if C = 1         | Unaifected      | Tests the state of the C-bit and causes a branch if C is set. It is used to test for a carry in the result of a previous operation.                                                                                                                                                                                                                                                              |

| Mnemonic    | OP Code | Operation | • | Condition Codes |

|-------------|---------|-----------|---|-----------------|

| JMP<br>Jump | 0001DD  | PC←(dst)  |   | Unaffected      |

SPL 00023N PS <7:5>  $\leftarrow$  priority N Unaffected Set Priority

Set Priority

Level

### Description

JMP provides more flexible program branching than provided with the branch instruction. Control may be transferred to any location in memory (no range limitation) and can be accomplished with the full flexibility of the addressing modes with the exception of register mode 0. Execution of a jump with mode 0 will cause an illegal instruction condition. (Program control cannot be transferred to a register.) Register deferred mode is legal and will cause program control to be transferred to the address held in the specified register. Note that instructions are word data and must therefore be fetched from an even numbered address. A boundary error trap condition will result when the processor attempts to fetch an instruction from an odd address.

The least significant three bits of the instruction are loaded into the Program Status Word(PS) bits 7-5 thus causing a changed priority. The old priority is lost.

Assembler syntax is: SPL N Note: This instruction is a no op in User and Supervisor modes.

Table 2-4 Program Control Instructions (Cont)

| Mnemonic                        | OP Code | Operation                                                                                                                                                                                               | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JRS Jump to subroutine          | 004RDD  | (tmp) ← (dst) (tmp is an inter- nal processor register) ↓ (SP) ← reg (push reg con- tents onto proces- sor stack) reg ← PC PC holds location fol- lowing JSR; this address PC ← (tmp), now put in (reg) | Unaffected      | In execution of the JSR, the old contents of the specified register (the linkage pointer) are automatically pushed onto the processor stack and new linkage information placed in the register. Thus, subroutines nested within subroutines to an depth may all be called with the same linkage register. There is no need either to plan the maximum depth at which any particular subroutine will be called or to include instructions in each routine to save and restore the linkage pointer. Further since all linkages are saved in a re-entrant manner on the processor stack, execution of a subroutine may be interrupted, and the same subroutine re-entered and executed by an interrupt service routine. Execution of the initial subreputine can then be resumed when other requests are satisfied. This process (called nesting) can proceed to any level. |

|                                 |         |                                                                                                                                                                                                         |                 | JSR PC, dst is a special case of the PDP-11 subroutine call suitable for subroutine calls that transmit parameters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RTS<br>Return from<br>abroutine | 00020R  | PC ← (reg)<br>(reg) ← SP †                                                                                                                                                                              | Unaffected      | Loads contents of register into PC and pops the top element of the processor stack into the specified register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                 |         |                                                                                                                                                                                                         |                 | Return from a non-re-entrant subroutine is typically made through the same register that was used in its call. Thus, a subroutine called with a JSR PC, dst exits with an RTS PC, and a subroutine called with a JSR R5, dst may pick up parameters with addressing modes (R5) +, X (R5), or @X (R5) and finally exit, with an RTS R5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mnemonic | OP Code | Operation             | Condition Codes                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                        |

|----------|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTI      | 000002  | PC+(SP)↑<br>PSW+(SP)↑ | <ul> <li>N: loaded from processor stack</li> <li>Z: loaded from processor stack</li> <li>V: loaded from processor stack</li> <li>C: loaded from processor stack</li> </ul> | Used to exit from an interrupt or trap service routine. The PC and PSW are restored (popped) from the processor stack. If the RTI sets the T-bit in the PSW, a trace trap will occur prior to executing the next instruction.                                                                                      |

| RTT      | 000006  | PC+(SP)†<br>PS+(SP)†  | N: loaded from processor stack Z: loaded from processor stack V: loaded from processor stack C: loaded from processor stack                                                | This is the same as the RTI instruction, except that it inhibits a trace trap, while RTI permits a trace trap. If a trace trap is pending, the first instruction after the RTT will be executed prior to the next "T" trap. In the case of the RTI instruction, the "T" trap will occur immediately after the RTI. |

In RTT and RTI, only transactions from more privileged processor modes to the same or less privileged modes are allowed. When executed in Supervisor mode, the new PSW bits cannot be Kernel. When executed in User mode, the new PSW mode bits can only be User.

Table 2-4 Program Control Instructions (Cont)

| Mnemonic | OP Code | Operation                                                                | Condition Codes | Description                                                                                                                                                                                                                                     |

|----------|---------|--------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MARK     | 0064NN  | SP ← SP + 2xnn<br>PC ← R5<br>R5 ← (SP) ↑<br>nn = number of<br>parameters | Unaffected      | Used as part of the standard PDP-11 subroutine return convention. MARK facilitates the stack cleanup procedures involved in subroutine exit. Assembler format is: MARK N  Example: MOV R5,-(SP) :place old R5 on stack                          |

|          |         |                                                                          |                 | MOV P1,-(SP) place N parameters on MOV P2,-(SP) the stack to be used parameters on the stack to be used productions.                                                                                                                            |

|          |         |                                                                          |                 | MOV PN,-(SP) splaces the instruction MOV #MARKN,-(SP) sMARK N on the stack set up address at black                                                                                                                                              |

|          |         |                                                                          |                 | MOV SP,R5 ;N instruction  JSR PC,SUB ;jump to subroutine                                                                                                                                                                                        |

|          |         |                                                                          |                 | At this point the stack is as follows:  OLD R5 P1 PN MARK N OLD PC                                                                                                                                                                              |

|          |         |                                                                          |                 | And the program is at the address SUB which is the beginning of the subroutine.  SUB: execution of the subroutine itself  RTS R5: ;the return begins                                                                                            |

|          |         | ·                                                                        |                 | This causes the contents of R5 to be placed in the PC which then results in the execution of the instruction MARK N. The contents of old PC are placed in R5                                                                                    |

|          |         | ,                                                                        |                 | MARK N causes: (1) the stack pointer to be adjusted to point to the old R5 value: (2) the value now in R5 (the old PC) to be placed in the PC, and (3) contents of the old R5 to be popped into R5, thus completing the return from subroutine. |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic                                               | OP Code               | Operation                                                                                 | Condition Codes                                                                                             | Description                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOB<br>Subtract one and<br>branch if not<br>equal to 0 | 077R00<br>plus offset | $R \leftarrow R - 1$ if this result $\neq$ 0 then PC $\leftarrow$ PC $-(2 \times offset)$ | Unaffected                                                                                                  | The register is decremented. If it is not equal to 0, twice the offset is subtracted from the PC (now pointing to the following word). The offset is interpreted as a six-bit positive number. This instruction provides a fast, efficient method of loop control. Assembler syntax is:  SOB R,A |

|                                                        |                       |                                                                                           |                                                                                                             | where A is the address to which transfer is to be made if<br>the decremented R is not equal to 0. Note that the SOB<br>instruction cannot be used to transfer control in the<br>forward direction.                                                                                               |

| PT<br>reak-point Trap                                  | 000003                | ↓ (SP) ← PS<br>↓ (SP) ← PC<br>PC ← (14)<br>PS ← (16)                                      | N: loaded from trap vector Z: loaded from trap vector V: loaded from trap vector C: loaded from trap vector | Performs a trap sequence with a trap vector address of 14. Used to call debugging aids. The user is cautioned against employing code 000003 in programs run under these debugging aids.                                                                                                          |

| OT<br>OT Trap                                          | 000004                | ↓ (SP) ← PS<br>↓ (SP) ← PC<br>PC ← (20)<br>PS − (22)                                      | N: loaded from trap vector Z: loaded from trap vector C: loaded from trap vector                            | Performs a trap sequence with a trap vector address of 20. Used to call the I/O executive routine IOX in the paper-tape software system and for error reporting in the disk operating system.                                                                                                    |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic             | OP Code             | Operation                                            | Condition Codes                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|---------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMT<br>Emulator Trap | 104000              | ↓ (SP) ← PS<br>↓ (SP) ← PC<br>PC ← (30)<br>PS ← (32) | N: loaded from trap vector Z: loaded from trap vector V: loaded from trap vector C: loaded from trap vector | All operation codes from 104000 to 104377 are EMT instructions and may be used to transmit information to the emulating routine (e.g., function to be performed). The trap vector for EMT is at address 30; the new central processor status (PS) is taken from the word at address 32.                                                                                           |

| RAP                  | 104400 to<br>104777 | ↓ (SP) ← PS<br>↓ (SP) ← PC<br>PC ← (34)<br>PS ← (36) | N: loaded from trap vector Z: loaded from trap vector V: loaded from trap vector C: loaded from trap vector | CAUTION EMT is used frequently by DEC system software and is therefore not recommended for general use.  Operation codes from 104400 to 104777 are TRAP instructions. TRAPs and EMTs are identical in operation, except that the trap vector for TRAP is at address 34.  NOTE  Since DEC software makes frequent use of EMT, the TRAP instruction is recommended for general use. |

NOTE: Condition Codes are unaffected by these instructions

<sup>\*</sup>DD = destination (address mode and register)

<sup>†(</sup>dst) = destination contents

Table 2-5 Miscellaneous Instructions (Cont.)

| Mnemonic | OP Code         | Operation                                                                                                     | Condition Codes | Description                                                                                                       |

|----------|-----------------|---------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------|

| WAIT     | 000001          | a Principal de Armania (n. 1879). Armania (n. 1884). Armania (n. 1884). Armania (n. 1884). Armania (n. 1884). | Unaffected      | Provides a way for the processor to relinquish use of the bus while it                                            |

|          |                 |                                                                                                               |                 | waits for an external interrupt. Having been given a WAIT command, the processor will not compete for bus         |

|          |                 |                                                                                                               |                 | by fetching instructions or operands<br>from memory. This permits higher<br>transfer rates between device and     |

|          |                 |                                                                                                               |                 | memory, as no processor-induced latencie will be encountered by bus requests from the device. In WAIT, as in all  |

|          |                 |                                                                                                               |                 | instructions, the PC points to the next instruction following the WAIT operation. Thus, when an interrupt         |

|          |                 |                                                                                                               |                 | causes the PC and PS to be pushed onto<br>the stack, the address of the next<br>instruction following the WAIT is |

|          |                 |                                                                                                               |                 | saved. The exit from the interrupt routine (i.e., execution of an RTI instruction) will cause resumption of       |

|          |                 |                                                                                                               | •               | the interrupted process at the instruction following the WAIT.                                                    |

| RESET    | 000005          | PC(SP)<br>PSW(SP)                                                                                             | Unaffected      | Sends INIT on the Unibus for 100 ms. All devices on the Unibus are reset to their state at power-up.              |

| MFPT     | 90007<br>976010 | RO<7:0>←                                                                                                      | Unaffected      | Upon execution, the MFPT instruction                                                                              |

|          |                 | Processor Code<br>Code 1<br>RO<15:8>+                                                                         |                 | returns to the low byte of RO a processor model code (octal 3 for PDP 11/68.)                                     |

|          |                 | Processor<br>Subcode                                                                                          |                 | The high byte of RO will be loaded with a processor specified subcode (octal Ø for PDP 11/68.                     |

Table 2-5 Miscellaneous Instructions (Cont.)